1. Jurnal[Back]

2. Alat dan Bahan[Back]

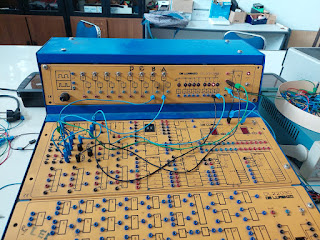

- . Module D’Lorenzo

- . Jumper

- Panel DL 2203C

- Panel DL 2203D

- Panel DL 2203S

- IC74LS90

- IC 7493

- Clock

- SPDT

- VCC

- Ground

- Logic Probe

3. Rangkaian Simulasi[Back]

4. Prinsip Kerja Rangkaian[Back]

switch dari B0,B1,B2,B3 dihubungkan dengan kaki input dari ic 74LS90 diman B0 dan B1 ke kaki R0 dan B2 dan B3 dihubungkan ke kaki R9 sedangkan CK A akan mengatur output Q0 dan CK B akan mengatur output dari Q1,Q2,Q3. agar counter berjalan dengan benar,maka CK B akan dihubungkan dengan output dari Q0. hasil masing-masing output akan dimasukan dalam decoder dan merubah nya menjadi 7 bit dan dihubungkan dengan common seven segmen anoda.

untuk switch dari B4 dan B5 akan dihubungkan dengan kaki input ic 7493 dimana B4 akan masuk ke kaki R0(1) dan B5 ke kaki R0(2). CK A akan mengatur output QA dan CK B akan mengatur output dari QB,QC,QD. agar counter berjalan dengan benar,maka CK B akan dihubungkan dengan output dari QA. hasil masing-masing output akan dimasukan dalam decoder dan mengubah nya menjadi output 7 bit lalu menghubungkannya dengan common seven ssegmen anoda. hasil output keluaran dari counter ini cepat.

5. Video Rangkaian[Back]

6. Analisa[Back]

1. Analisa output percobaan berdasarkan ic yang digunakan?

jawab

output yang dikeluarkan oleh ic 74ls90 dan ic 7493 jika pada kondisi aktif maka akan menghasilkan counter up,untuk ic 74ls90 memiliki counter bit 0-9 dan memiliki output 4 bit, sedangkan untuk ic 7493 memiliki counter bit 0-15 dan memiliki output 4 bit.

2. Analisa hasil kondisi 3 pada percobaan 2b?

jawab

pada kondisi 3, bisa kita lihat bahwa ketika B3 bernilai 1 dan B4 bernilai 1 maka masing-masing ic akan aktif karena konsep pada ic memiliki gerbang nand, sehingga akan terjadi counter up.

3. Apa pengaruh Clock A dan Clock B pada ic yang digunakan ?

jawab

clock A berpengaruh dan mengatur output dari Q0, sedangkan clock B akan mengatur output dari Q1,Q2,dan Q3, untuk tidak terjadi ketidakaturan counter maka kaki clock B akan dihubungkan ke output Q0 sehingga akan dihasilkan output yang beraturan dan terjadi counter up.

7. Link Download[Back]

Tidak ada komentar:

Posting Komentar