1. Jurnal[Back]

2. Alat dan Bahan[Back]

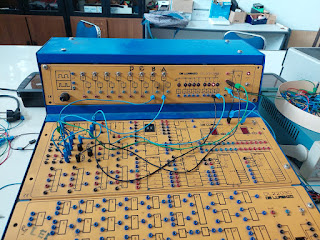

- . Module D’Lorenzo

- . Jumper

- Panel DL 2203C

- Panel DL 2203D

- Panel DL 2203S

- JK Flip-Flop

- D Flip-Flop

- Clock

- SPDT

- VCC

- Ground

- Logic Probe

3. Rangkaian Simulasi[Back]

4. Prinsip Kerja Rangkaian[Back]

pada percobaan ini terdapat JK flip-flop yang terhubung dengan vcc dan kaki lainnya ke ground. pada B0 berlogika 0 sehingga diteruskan ke kaki reset dan mengubah menjadi logika 1 dan menghasilkan output 1, sedangkan pada B1 berlogika 1 diteruskan ke kaki set dan mengubah menjadi logika 0 dan menghasilkan output 0. kondisi ini disebut dengan kondisi reset. sedangkan untuk J,K,clock nya tidak memengaruhi apapun

5. Video Rangkaian[Back]

6. Analisa[Back]

1. Apa yang terjadi jika B1 diganti CLK pada kondisi 2?

jawab:

tidak akan terjadi apa-apa,jika clock terhuibung dengan clock dan tidak terjadi trigger.hal ini tidak akan merubah output karena input pada J dan K akan selalu berubah bersamaan.

2. Bandingkan hasil percobaan dengan teori!

jawab:

seluruh percobaan yang dilakukan sesuai dengan teori yang ada,dimana jika B=0 dan B1=1 maka dihasilkan output Q=0 dan Q'=1. jika B0=1 dan B1=0 maka menghasilkan output Q=1 dan Q'=0. dan jika input sama sama 0 maka akan menghasilkan input sama sama 1. untuk B0=1 dan B1=1 maka di pasangkan clock yang berguna untuk mengatur arus dan beda outputnya akan menghasilkan output yang bergantian atau bisa disebut dengan kondisi toggle

3. Apa fungsi masing-masing kaki Flip-Flop yang digunakan?

jawab:

pada flip-flop, kaki R dan S merupakan penentu utama dari output, namun jika R dan s dialiri ke vcc dan menyebabkan tidak aktif maka output penentu nya dalah melalui kaki J,K dan clock yang akan menentukan berbagai macam kondisi yang ada sesuai dengan tabel kebenaran.

7. Link Download[Back]

download video [disini]

download gambar [disini]

.jpeg)

Tidak ada komentar:

Posting Komentar