1. Jurnal[Back]

2. Alat dan Bahan[Back]

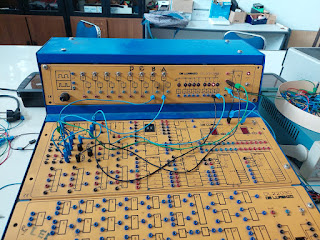

- . Module D’Lorenzo

- . Jumper

- Panel DL 2203C

- Panel DL 2203D

- Panel DL 2203S

- JK Flip-Flop

- D Flip-Flop

- Clock

- SPDT

- VCC

- Ground

- Logic Probe

3. Rangkaian Simulasi[Back]

4. Prinsip Kerja Rangkaian[Back]

A. Rangkaian JK flip-flop

Pada percobaan ini, didapat kan prinsip kerja bahwa kaki dari reset terhubung langsung menuju B0=0 sehingga arus langsung mengarah ke ground sehingga ketika masuk ke dalam kaki reset, logika nya berubah menjadi 1 dan mempunyai output 1 sedangkan untuk B1=1 arus langsung mengalir menuju vcc sehingga ketika masuk ke dalam kaki set logikanya berubah menjadi 0 dan tmempunyai output 0,sehingga disebut pada kondisi ini adalah kondisi reset karena hanya pada kaki reset yang berlogika 1. untuk J,K dan clock pada kondisi ini tidak menyebabkan pengaruh dan perubahan apapun.

B. Rangkaian D flip-flop

pada percobaan ini, B0 berlogika 0 sehingga arus langsung mengalir ke ground, ketika arus masuk di kaki reset logika nya berubah menjadi logika 1 dan mempunyai output akhir 1. sedangkan untuk B1 berlogika 1 arus mengalir menuju vcc dan ketika di kaki set berubah menjadi logika 0 dan mempunyai output 0. sehingga kondisi ini disebut kondisi reset. untuk D dan clock tidak memengaruhi apapun.

p sama - sama menghasilkan output yang sma pada Q\\

5. Video Rangkaian[Back]

6. Analisa[Back]

1. Bagaimana jika B0 dan B1 sama sama diberi logika 0, apa yang terjadi pada rangkaian?

jawab:

sesuai pada percobaan,maka output yang dihasilkan pada JK flip-flop sama -sama menghasilkan output yang sama pada Q maupun di Q, yaitu 0

2. Bagaimana jika B3 diputuskan/tidak dibubungkan pada rangkaian apa yang terjadi pada rangkaian?

jawab:

untuk 3 kondisi pertama,B3 bersifat dont care sehingga jika tidak dihubungkan tidak akan mengubaah apapun,namn pada kondisi 4,5,6,7 clock atau B3 berfungsi sebagai pengatur jalan nya arus yang masuk. jika tidak ada clock maka output pad Q maupun di Q' tidak aakan berubah.

3. Jelaskan apa yang dimaksud kondisi toggle, kondisi not change, dan kondisi terlarang pada Flip-Flop!

jawab:

- kondisi toggle adalah kondisiyang ada pada JK flip-flop yang mana inputnya sama sama 1 dan memiliki clock,sehingga clock disini berfungsi sebagai pengatur masuk nya arus,sehinga mengakibatkan output akan berpindah-pindah

- kondisi not change adalah kondisi dimana output tidsk mengalami perubahan

- kondisi terlarang adalah kondisi pada RS flip-flop yang mempunyai input sama-sama 1 dan tidak mempunyai clock,hal ini akan mengakibaatkan kerusakan atau error.

7. Link Download[Back]

Tidak ada komentar:

Posting Komentar